Компания TSMC на этой неделе уже анонсировала освоение новоиспеченной ступени литографических технологий, получившей условное обозначение N6. В пресс-релизе сообщалось, что данная ступень литографии будет доведена до стадии рискового производства к первому кварталу 2020 года, но лишь стенограмма квартальной отчётной конференции TSMC позволила узнать новые подробности о сроках освоения так называемой 6-нм технологии.

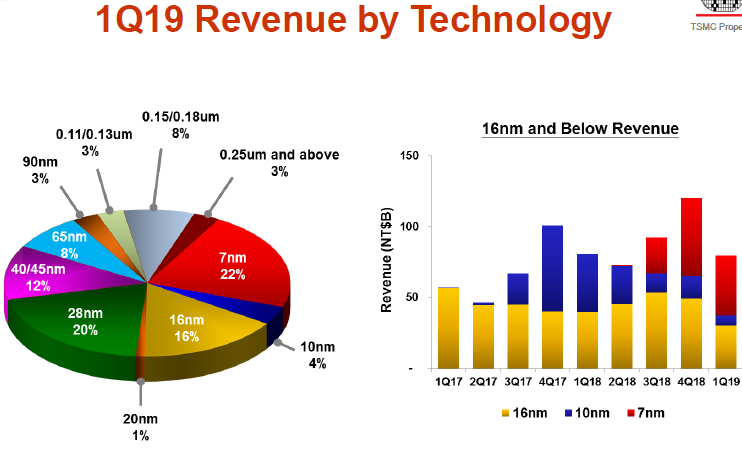

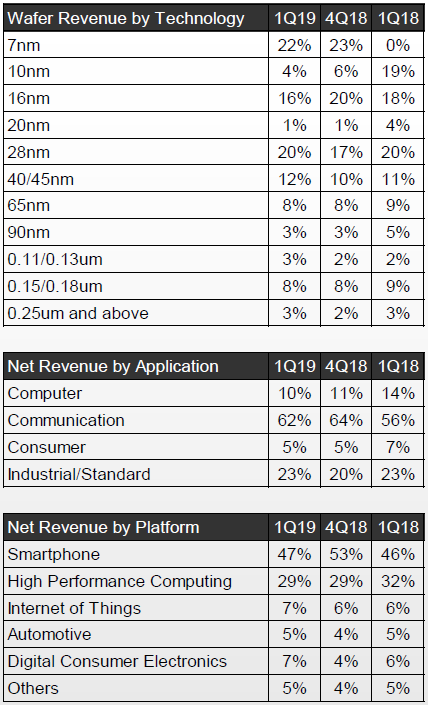

Вытекает напомнить, что TSMC уже серийно выпускает широкую номенклатуру 7-нм изделий — в минувшем квартале они формировали 22 % выручки компании. По прогнозам руководства TSMC, в льющемся году на долю техпроцессов N7 и N7+ будет приходиться не менее 25 % выручки. Второе поколение 7-нм техпроцесса (N7+) подразумевает немало широкое применение литографии со сверхжёстким ультрафиолетовым излучением (EUV). В то же время, как подчёркивают представители TSMC, именно полученный при внедрении техпроцесса N7+ эксперимент позволил компании предложить клиентам техпроцесс N6, который полностью повторяет по экосистеме проектирования N7. Это позволяет разработчикам в кратчайшие сроки и с минимальными физическими затратами перейти с N7 или N7+ на N6. Генеральный директор Си Си Вэй (C.C. Wei) на квартальной конференции даже выразил уверенность, что все клиенты TSMC, использующие 7-нм техпроцесс, перебегут на использование 6-нм технологии. Ранее он в аналогичном контексте упоминал о готовности «почти всех» пользователей 7-нм техпроцесса TSMC мигрировать на 5-нм техпроцесс.

Уместно будет пояснить, какие преимущества обеспечивает 5-нм техпроцесс (N5) в исполнении TSMC. Как сознался Си Си Вэй, по продолжительности жизненного цикла N5 будет одним из самых «долгоиграющих» в истории компании. При этом от 6-нм техпроцесса с точки зрения разработчика он будет существенно выделяться, поэтому переход на 5-нм нормы проектирования потребует существенных усилий. Например, если 6-нм техпроцесс по сравнению с 7-нм обеспечивает увеличение плотности размещения транзисторов на 18 %, то разница между 7-нм и 5-нм будет достигать 80 %. С иной стороны, прирост быстродействия транзисторов при этом не превысит 15 %, так что тезис о замедлении действия «закона Мура» в этом случае подтверждается.

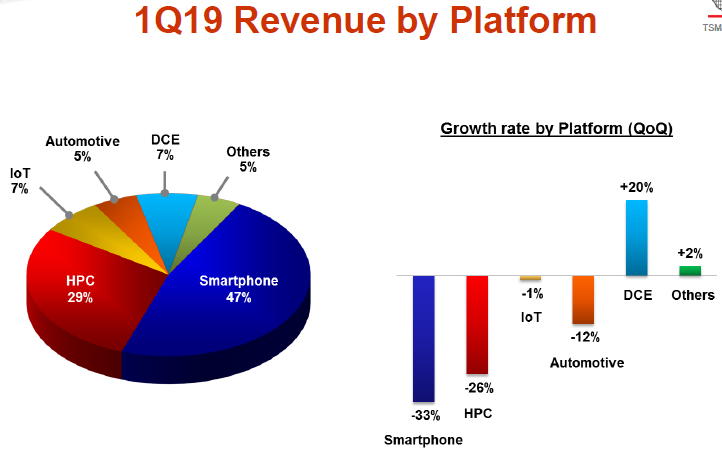

Всё это не мешает главе TSMC утверждать, что техпроцесс N5 будет «самым конкурентоспособным в отрасли». С его помощью компания рассчитывает не лишь увеличить свою долю рынка в существующих сегментах, но и привлечь новых клиентов. В контексте освоения 5-нм техпроцесса особые чаяния возлагаются на сегмент решений для высокопроизводительных вычислений (HPC). Сейчас на его долю приходится не более 29 % выручки TSMC, а 47 % выручки приносят компоненты для смартфонов. Со порой доля сегмента HPC должна будет увеличиваться, хотя и разработчики процессоров для смартфонов будут охотно осваивать новоиспеченные литографические нормы. Развитие сетей поколения 5G тоже станет одной из причин роста выручки в ближайшие годы, находят в компании.

Наконец, из уст генерального директора TSMC прозвучало подтверждение начала выпуска серийной продукции с применением техпроцесса N7+, использующего EUV-литографию. Степень выхода годной продукции по этому техпроцессу сопоставим с 7-нм технологией первого поколения. Внедрение EUV, по словам Си Си Вэя, не может гарантировать моментальной экономической отдачи — пока затраты достаточно высоки, но как только производство «наберёт обороты», себестоимость продукции начнёт снижаться типическими для последних лет темпами.